# Low No-Load Current, AM Suppression Function, with Master-Slave Mode, 2X75W Stereo Class D Audio Amplifier

#### **General Description**

CS8685H is a 2X75W Stereo Class D audio amplifier; This device is designed with a heat dissipation pad on the top. When the heat sink is connected to the pad, it can output a maximum continuous power of 2X75W under the power supply voltage of 24V; Through the setting of master-slave mode, CS8685H can realize infinite cascade, so as to realize multi-channel output of the system; CS8685H has advanced EMI suppression technology. It uses surface mount technology and requires only a small number of peripheral devices to enable the system to have highquality audio output power. Cs8685h has built-in overcurrent protection, short circuit protection and overheating protection, which effectively protects the chip from being damaged under abnormal working conditions. The CS8685H can achieve a maximum efficiency of more than 95%, and the withstand voltage design of more than 40V provides ultra-high reliability for the chip, which can effectively reduce the proportion of defects in the production process. CS8685H provides a special EQB32 package form for customers to choose. The appropriate package size provides the greatest convenience for customers to install heat sinks. Its rated working temperature range is - 40 °C to 85 °C.

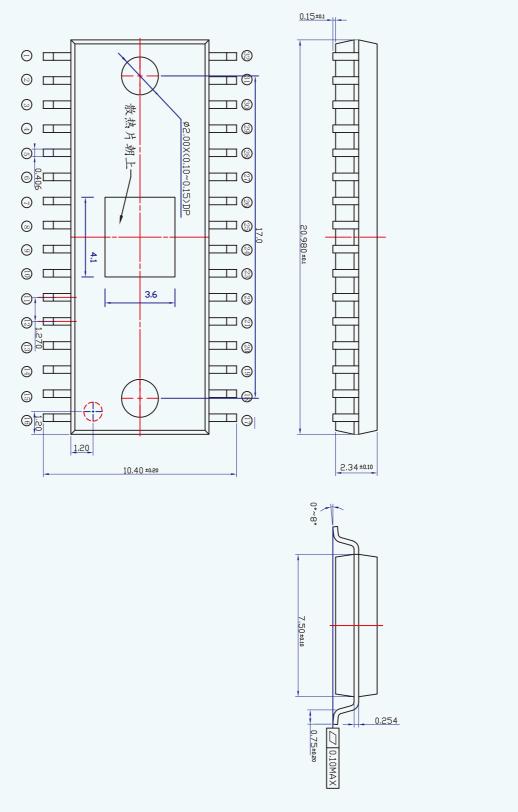

#### **Package**

• EQB32

#### **Features**

Output Power

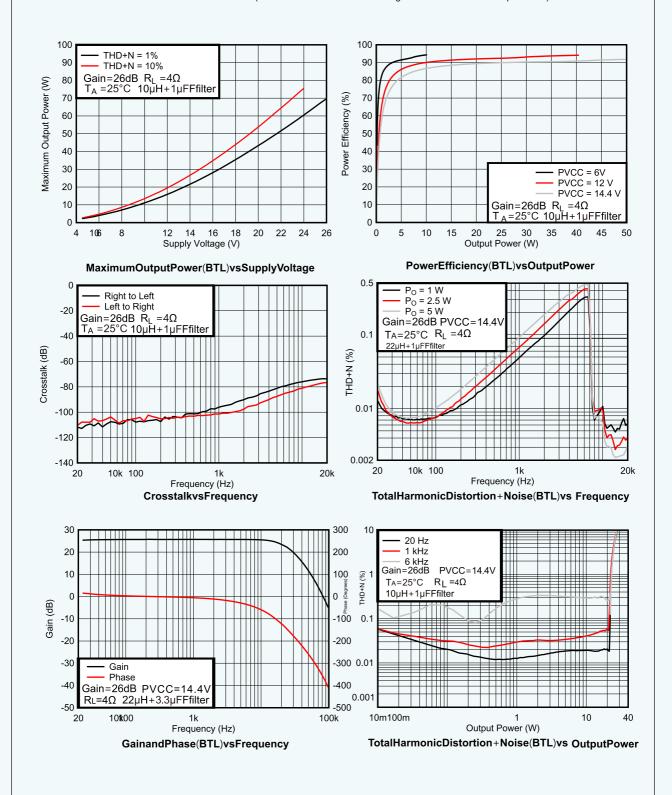

VDD =  $24V@RL = 4\Omega$  THD+N=10% Po=2X75W VDD =  $24V@RL = 4\Omega$  THD+N=1% Po=2X62WVDD =  $26V@RL = 4\Omega$  THD+N=1% Po=2X70W  $VDD = 28V@RL = 6 \Omega THD+N=1\% Po=2X60W$

- Single Power Supply, Wide Power Supply Voltage Range: 5V~28V

- Audio System with Filter Network, Static Current 50mA@24V

- High Reliability Design: 40V with Stand Voltage Design

- Efficiency: 95%@PVCC=26V RL = 8Ω PO=2X20W

- Four Segment Gain (Optional)

- Mute Function Control

- Master Slave Mode Programmable Control, Realize Infinite Cascade Power Output

- Multiple Switching Frequency Options: AM Suppression Function

- Programmable Power Limit

- Good Short Circuit Protection and Temperature Protection with Automatic Recovery Function

- Good Distortion and Anti POP Function

- Enhanced Package Design: Special Design of Top **Heat Dissipation Pad**

- Meet The Application Requirements of Automobile

#### **Applications**

- Car Audio

- Home Audio System

- Emergency Call

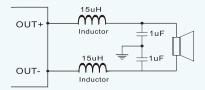

- It is recommended to select the output inductance with saturation current above 6A.

- The gain terminal is grounded, integrating 12K input resistance and 650K feedback resistance; The gain terminal is suspended, integrating a 15.2K input resistor and a 610K feedback resistor; Gain terminal is connected to high level, integrating 25.5K input resistance and 510K feedback resistance

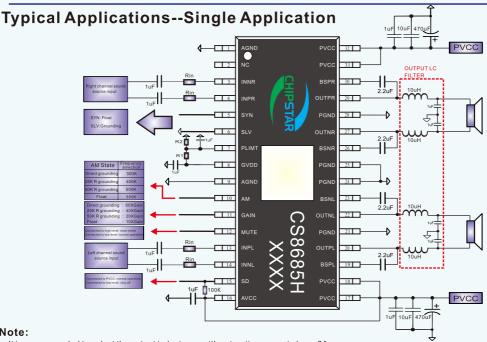

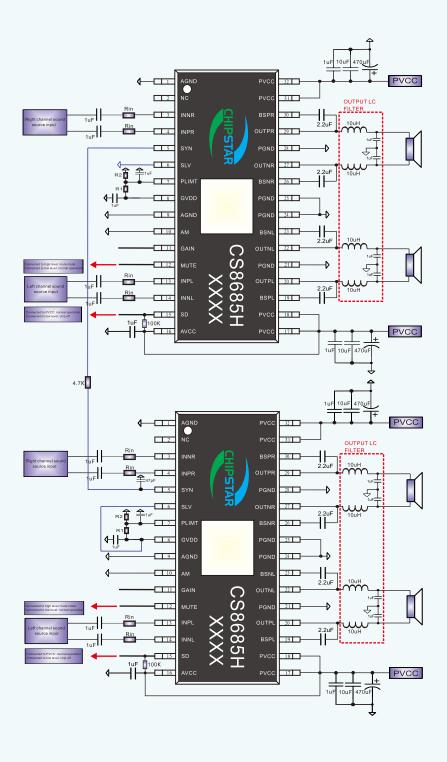

# Typical Applications--Master Slave Mode Application

# PIN Configuration and Functions

#### Note:

- The above figure is a top view

- The white frame in the figure is the top heat sink

| NO.         | NAME  | TYPE | DESCRIPTION                                                                                                                  |

|-------------|-------|------|------------------------------------------------------------------------------------------------------------------------------|

| 1           | AGND  | Р    | Analog ground                                                                                                                |

| 21,24,25,28 | PGND  | Р    | Power ground                                                                                                                 |

| 2           | NC    | Р    | Empty                                                                                                                        |

| 3           | INNR  | I    | Right channel audio input negative terminal                                                                                  |

| 4           | INPR  | I    | Right channel audio input Positive terminal                                                                                  |

| 5           | SYN   | I/O  | The clock input/output pin is used to synchronize multiple chip The synchronization direction is determined by the SLV pin   |

| 6           | SLV   | I    | The master-slave mode selection pin is connected to the low to select the master chip, and the high to select the slave chip |

| 7           | PLIMT | ı    | Output power limit pin                                                                                                       |

| 8           | GVDD  | l    | Driving voltage of upper tube gate                                                                                           |

| 9           | AGND  | Р    | Analog ground                                                                                                                |

| 10          | AM    | ı    | Am frequency control pin                                                                                                     |

| 11          | GAIN  | ı    | Gain control pin                                                                                                             |

| 12          | MUTE  | ı    | Mute mode control pin                                                                                                        |

| 13          | INPL  | l    | Left channel audio input Positive terminal                                                                                   |

| 14          | INNL  | ĺ    | Left channel audio input negative terminal                                                                                   |

| 15          | SD    | ı    | Turn off control pin                                                                                                         |

| 16          | AVCC  | Р    | Analog power supply                                                                                                          |

| 17,18,31,32 | PVCC  | Р    | Power supply                                                                                                                 |

| 19          | BSPL  | ı    | Left channel positive output upper tube bootstrap                                                                            |

| 20          | OUTPL | 0    | Left channel audio output Positive terminal                                                                                  |

| 22          | OUTNL | 0    | Left channel audio output negative terminal                                                                                  |

| 23          | BSNL  | ı    | Left channel negative output upper tube bootstrap                                                                            |

| 26          | BSNR  | ı    | Right channel negative output upper tube bootstrap                                                                           |

| 27          | OUTNR | 0    | Right channel audio output negative terminal                                                                                 |

| 29          | OUTPR | 0    | Right channel audio output Positive terminal                                                                                 |

| 30          | BSPR  |      | Right channel positive output upper tube bootstrap                                                                           |

**Functional Block Diagram** Modulation and PBTLSelect Gate Drive PWM Logic GND АМ PLIMIT PVCC BSNL AVCC GVDD OUTNL. FB PWM Logic OUTPL\_FB OUTPL OUTPL\_FB GND Thermal Pad

# **Absolute Maximum Ratings** <sup>1</sup>

| SYMBOL            | PARAMETER                            | VALUE   | UNIT |

|-------------------|--------------------------------------|---------|------|

| Power supply      | PVCC                                 | -0.3~40 | V    |

|                   | SD                                   | -0.3~40 | V    |

| Input pin voltage | GAIN,PLIMT,AM,MUTE,SYN,SLV           | -0.3~5  |      |

|                   | INN,INP                              | -0.3~5  |      |

| T <sub>A</sub>    | Operating temperature range          | -40~85  | °C   |

| TJ                | Junction operating temperature range | -40~150 | °C   |

| T <sub>STG</sub>  | Storage temperature range            | -60~150 | °C   |

**Recommended Operating Conditions**

| SYMBOL           | PARAMETER                            | VALUE    | UNIT       |

|------------------|--------------------------------------|----------|------------|

| PV <sub>CC</sub> | supply voltage                       | 5~30     | V          |

| T <sub>J</sub>   | Junction operating temperature range | -40~ 125 | ℃          |

| T <sub>A</sub>   | Ambient temperature range            | -40~85   | $^{\circ}$ |

# Thermal Information <sup>2</sup>

| SYMBOL          | PARAMETER                                                               |    | UNIT |

|-----------------|-------------------------------------------------------------------------|----|------|

| Өја             | Package thermal resistance - chip to environment thermal resistance     | 25 | °C/W |

| θ <sub>JC</sub> | Package thermal resistance - chip to package surface thermal resistance | 7  | °C/W |

# **Ordering Information**

| Product Name | Package Type | Device Marking | Packing Types | Quantity |

|--------------|--------------|----------------|---------------|----------|

| CCCCCELL     | EOD22        |                | Tube          | 20       |

| CS8685H      | EQB32        | ****           | Таре          | 1000     |

# **ESD Range**

| HBM (Human Body Model | ) | ±2kV  |

|-----------------------|---|-------|

| MM (Machine model)    |   | ±200V |

<sup>1.</sup> The above parameters are only the limit values of device operation. It is not recommended that the working conditions of the device exceed the limit values. Otherwise, the reliability and life of the device will be affected, and even permanent damage will be caused.

**Recommended Operating Conditions**

|                 | DESCRIPTION              | TEST CONDITIONS                       | MIN | MAX | UNIT |

|-----------------|--------------------------|---------------------------------------|-----|-----|------|

| $V_{CC}$        | Power supply             | PVCC                                  | 5   | 28  | ٧    |

| V <sub>IH</sub> | Input high level         | SD,MUTE,AM,PLIMT,GAIN,SYN,SLV         | 1.5 |     | ٧    |

| V <sub>IL</sub> | Input low level          | SD,MUTE,AM,PLIMT,GAIN,SYN,SLV         |     | 0.3 | ٧    |

| I <sub>IH</sub> | High level input current | SD,MUTE,AM,PLIMT,GAIN,Vi=2V,Vcc=20V   |     | 50  | uA   |

| I <sub>IL</sub> | Low level input current  | SD,MUTE,AM,PLIMT,GAIN,V:=0.2V,Vcc=20V |     | 5   | uA   |

| OVP             | Overvoltage protection   |                                       |     | 40  | ٧    |

# **DC Parameters**

| DESCRIPTION                            |                       | TEST CONDITIONS                                 |                   | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------|-----------------------|-------------------------------------------------|-------------------|------|------|------|------|

| Vos                                    | Output offset voltage | V <sub>IN</sub> =0V , GAIN=36dB                 |                   |      | 6    | 15   | mV   |

| I <sub>CC</sub>                        | Quiescent current     | SD=2V,4 $\Omega$ loudspeaker , PV <sub>CC</sub> | =24V              |      | 50   | 60   | mA   |

| I <sub>CC(SD)</sub>                    | Standby current       | SD=0V,No load and filtering,PVc                 | <sub>C</sub> =24V |      | 20   | 30   | uA   |

| _                                      | Drain source          | V <sub>CC</sub> =21V,I <sub>O</sub> =500mA,     | Upper tube        |      | 80   |      | 5    |

| r <sub>DS(on)</sub>                    | on resistance         | T <sub>J</sub> =25°C                            | Lower tube        |      | 80   |      | mΩ   |

| t <sub>on</sub>                        | Turn on time          | SD=2V                                           |                   |      | 220  |      | ms   |

| t <sub>OFF</sub>                       | Turn off time         | SD=0V                                           |                   |      | 4    |      | us   |

| GVDD                                   | Gate drive voltage    | I <sub>GVDD</sub> =100 mA                       |                   | 4.25 | 4.75 | 5.25 | V    |

|                                        |                       | AM Direct grounding                             |                   | 270  | 300  | 330  |      |

| f <sub>OSC</sub> Oscillation frequency |                       | AM Grounded through 25K resistance              |                   | 360  | 400  | 440  | KHz  |

|                                        |                       | AM Grounded through 50K resistance              |                   | 450  | 500  | 550  | KIIZ |

|                                        |                       | AM Float                                        |                   | 500  | 550  | 600  |      |

AC Parameters

| <u>AC I</u> | AC Parameters                              |                     |                                      |                                       |        |        |        |        |

|-------------|--------------------------------------------|---------------------|--------------------------------------|---------------------------------------|--------|--------|--------|--------|

|             | <b>DESCRIPTION</b> TEST CONDITION          |                     |                                      | ONS                                   | MIN    | TYP    | MAX    | UNIT   |

| KSVF        | Power ripple reje                          | ction ratio         | 1kHz, 200mVpp Ripple, Gain=20dB,     | Input AC coupled to ground            |        | 70     |        | dB     |

| THD+        | N Total harmonic disto                     | rtion + noise       | PVcc=24V, f=1KHz, Po                 | =20W                                  |        | 0.05   |        | %      |

| Vn          | Output noise                               |                     | 20~22KHz, Aweight, Ga                | in = 20dB                             |        | 100    |        | uV     |

| VII         | Output noise                               | ;                   | 20 ZZIKIIZ, AWGIGIRI, Ga             | III — 200B                            |        | -78    |        | dBV    |

|             | Efficiency                                 |                     | PVcc=26V,f=1kHz,RL=8                 | Ω, Po=2X20W                           |        | 95     |        | %      |

| SNR         | Signal to noi                              | se ratio            | Maximum output at gain = 20dB        | , THD+N < 1% , f=1kHz                 |        | 102    |        | dB     |

| Therm       | al protection tem                          | perature            |                                      |                                       |        | 170    |        | °C     |

|             | Hysteresis tem                             | perature            |                                      |                                       |        | 15     |        | °C     |

|             |                                            | V <sub>DD</sub> = 2 | 22V@RL = 4Ω                          | THD+N=10%@Po=2X62W THD+N=1%@Po=2X50W  |        |        |        |        |

|             |                                            | V <sub>DD</sub> = 1 | 24V@RL = 4Ω                          | THD+N=10% @Po=2X75W THD+N=1%@Po=2X62W |        |        |        | =2X62W |

|             | $V_{DD} = 26V@RL = 4\Omega$                |                     | THD+N=1% @Po=2                       | 2X70W                                 |        |        |        |        |

| Ро          | Output power V <sub>DD</sub> = 28V@RL = 6Ω |                     | THD+N=10%@Po=2X73W THD+N=1%@Po=2X60W |                                       |        | =2X60W |        |        |

|             | $V_{DD} = 28V@RL = 8\Omega$                |                     | THD+N=10%@Po=22                      | X56W T                                | HD+N=1 | %@Po=  | =2X45W |        |

|             |                                            |                     |                                      |                                       |        |        |        | 1      |

# Electrical Characteristics ( All tests are based on 1KHz signals unless otherwise specified )

# Application Points 1. Overview

CS8685H is a 2X75W Stereo Class D audio amplifier; This device is designed with a heat dissipation pad on the top. When the heat sink is connected to the pad, it can output a maximum continuous power of 2X75W under the power supply voltage of 24V; Through the setting of master-slave mode, CS8685H can realize infinite cascade, so as to realize multi-channel output of the system; CS8685H has advanced EMI suppression technology. It uses surface mount technology and requires only a small number of peripheral devices to enable the system to have highquality audio output power. CS8685H has built-in overcurrent protection, short circuit protection and overheating protection, which effectively protects the chip from being damaged under abnormal working conditions. The CS8685H can achieve a maximum efficiency of more than 93%, and the withstand voltage design of more than 40V provides ultra-high reliability for the chip, which can effectively reduce the proportion of defects in the production process.

#### 2. Gain Setting

CS8685H is set with gain control pin gain. The following table shows the gain control mode of CS8685H and the corresponding integrated input and feedback resistance values.

| GAIN State       | Magnification | Input Res | Feedback Res |

|------------------|---------------|-----------|--------------|

| Direct grounding | 60X           | 9K        | 540K         |

| 25K R grounding  | 40X           | 13.5K     | 540K         |

| 50K R grounding  | 20X           | 23K       | 460K         |

| Float            | 10X           | 36K       | 360K         |

# 3. Short Circuit Protection and Automatic Recovery CS8685H protects the overcurrent state caused by short circuit at the output end. In case of short circuit, CS8685H immediately closes the output. After the short circuit fault at the output end is eliminated, CS8685H only needs to wait 110ms to recover itself.

#### 4. Temperature Protection

The temperature protection of CS8685H is to prevent device damage when the temperature exceeds  $170^{\circ}\text{C}$ . There is an upper and lower allowable range of  $\pm$   $15^{\circ}\text{C}$  between devices at this temperature point. Once the temperature exceeds the set temperature point, the device enters the closed state without output. When the temperature drops by  $20^{\circ}\text{C}$ , the temperature protection will be eliminated and the device starts to work normally.

#### 5. Mute Function and Shutdown Control

When the CS8685H works normally, the SD input port should be high potential. When the SD is pulled to the low potential, the output is turned off, the circuit enters the standby mode, and the SD terminal can be connected to PVCC at most The mute input port should

be low potential when the CS8685H works normally. When the mute is pulled to the high potential, the CS8685H output stage is turned off, the CS8685H enters the mute mode, and the maximum withstand voltage of the mute terminal is 5V.

#### 6. AM Suppression Function

CS8685H realizes the selection of MOS switching frequency through the control of AM pin, as shown in the table below:

| AM Status         | Frequency |

|-------------------|-----------|

| Direct grounding  | 300KHz    |

| 25K Res grounding | 400KHz    |

| 50K Res grounding | 500KHz    |

| Float             | 550KHz    |

#### 7. Power Limit

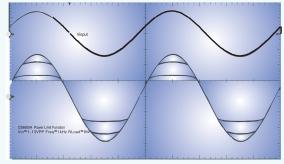

The principle of power limiting function is to limit the maximum duty cycle of power amplifier output PWM, so as to limit the maximum output power. The user can control the value of the maximum duty cycle by setting the voltage on the PLIMIT pin, so as to determine the set value of the maximum power. The result obtained by the power limiting method of limiting the maximum duty cycle is the same as reducing the PVCC supply voltage, and the output waveform is the clipping waveform with distortion, as shown in the figure. When the power is limited, if the input analog signal is further increased, the distortion of the output waveform will increase and the power will rise slowly. A voltage dividing resistor can be added between GVDD and the ground to set the voltage of pin 7 (PLIMIT) to limit the output power. The higher the voltage of pin 7, the greater the allowable output power. Add a 1uF capacitor from pin 7 to the ground.

CS8685H power limit waveform

#### 8. Master Slave Mode and Clock Control

The master-slave mode of the CS8685H is set through the pin SLV. When the SLV is grounded, the current CS8685H is the main chip. At this time, the internal clock works, and the syn pin outputs the internal clock signal to the outside, which is used to synchronize other CS8685H to work together. The clock of the master chip selects the frequency size through am. When the SLV pin is connected high, it is selected as the slave chip. The CLK inside the slave chip stops

working, and the SYN is switched to the receiving pin, which is locked synchronously by the internal PLL and the external frequency. SYN is a bidirectional IO, which can output CLK square wave or receive CLK square wave. When using SLV and syn, the following should be noted:

- SLV and SYN are low-voltage pins, and the maximum voltage should not exceed 5V;

- When only one CS8685H is used (master-slave synchronization is not required), SLV is grounded, SYN is suspended, and SYN always has signal output;

- The slave chip syn must be connected to the syn of the master chip. Otherwise, the slave chip does not work:

- There are scope requirements for clock synchronization of the slave chip. It is necessary to set the AM gear to be consistent with that of the master chip. For example, the master chip selects the

master chip. For example, the master chip selects the AM frequency as 300KHz, and syn outputs the 300KHz signal. The slave chip should also select the 300KHz gear in am. Otherwise, the PLL inside the slave chip may be unlocked.

#### 9. Inductance and Capacitance

CS8685H needs to load inductor and filter capacitor at the output end. It is recommended that the inductance should reach a saturation current of more than 6A during use. The specific parameters are shown in the figure below:

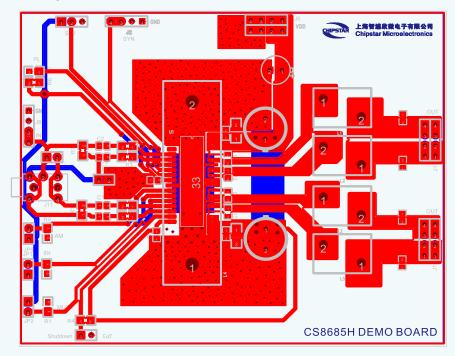

### **CS8685H PCB Design Guide**

In order to provide reliable design performance of the audio system, please pay special attention to the following points when designing the PCB layout of CS8685H:

- The large current path of the chip is:Vin → chip PVCC → GND.

- The routing rule of large current path is as thick as possible to reduce the impedance caused by PCB routing.

- The power supply pin of CS8685H must be pasted with two ceramic capacitors 10uF and 1uF, and be as close to the chip pin as possible. 470uF/50V is recommended for power supply electrolytic capacitor.

- All GNDS, including the GND of each capacitor, should be well connected, which can be connected to the copper foil of large-area GND nearby to reduce the ground loop impedance and inductance as much as possible. Demo example is shown in the figure.

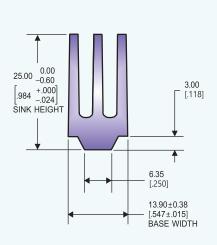

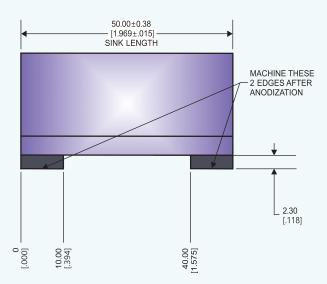

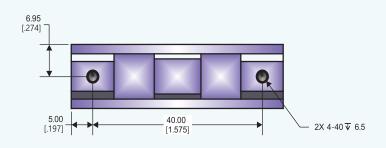

# **Description of Cooling Fins of Demo**

The heat sink used on EVB of CS8685H is 14mm × 25mm × 50mm, aluminum radiator, with the following dimensions:

# 封装信息

CS8685H EQB32 (170x150)Package Outline Dimensions units:mm