## OVERVOLTAGE AND OVERCURRENT PROTECTION IC AND Li+ CHARGER FRONT-END PROTECTION IC WITH LDO MODE

#### **DESCRIPTION**

The CS5805S is highly integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage,. The output acts as a linear regulator. The output is regulated to  $V_{\text{O(REG)}}$  for inputs between  $V_{\text{O(REG)}}$  and the overvoltage threshold. If an input overvoltage condition occurs, the IC immediately removes power from the charging circuit by turning off an internal switch. In the case of an overcurrent condition, it limits the system current at the threshold value, and if the overcurrent persists, switches the pass element OFF after a blanking period. Additionally, the IC also monitors its own die temperature and switches off if it exceeds 140°C. The input overcurrent threshold is user-programmable.

#### **FEATURES**

- Provides Protection for Three Variables:

- -Input Overvoltage, with Rapid Response in < 1µs -User-Programmable Overcurrent with Current Limiting

- · 30V pports up to 1.0A Input Current

- Robust Against False Triggering Due to Current Transients

- · Thermal Shutdown

- · Enable Input

- 5.45V LDO Mode Voltage Regulation

#### **APPLICATIONS**

- · Mobile Phones and Smart Phones PDAs

- MP3 Players

- · Low-Power Handheld Devices

- Bluetooth™ Headsets

#### **Package**

SOT23\_6L

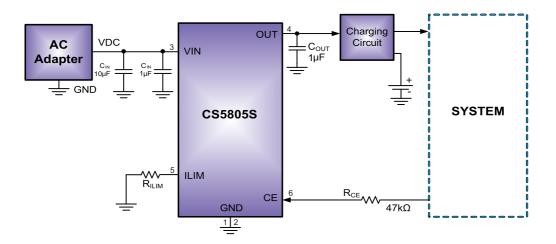

#### **TYPICAL APPLICATION CIRCUIT**

Figure a. Typical Application Circuit

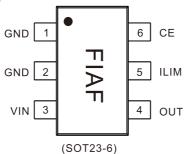

#### PIN CONFIGURATION (TOP VIEW)

#### **TERMINAL FUNCTIONS**

| TERMINAL |     | I/O | DESCRIPTION                                                                                                                                                                    |  |  |

|----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | PIN | 1/0 | DESCRIPTION                                                                                                                                                                    |  |  |

| GND      | 1   | _   | Ground                                                                                                                                                                         |  |  |

| GND      | 2   | _   | Ground                                                                                                                                                                         |  |  |

| VIN      | 3   | ı   | Input power. Connect IN to the external DC supply. Bypass IN to GND with a 1µF ceramic capacitor (minimum).                                                                    |  |  |

| OUT      | 4   | 0   | Output terminal to the charging system. Connect OUT to the external load circuitry. Bypass OUT to $_{\text{GND}}$ with a $_{\text{I}\mu\text{F}}$ ceramic capacitor (minimum). |  |  |

| ILIM     | 5   | I   | Input overcurrent threshold programming. Connect a resistor from ILIM to GND to set the overcurrent threshold.                                                                 |  |  |

| CE       | 6   | Ī   | Chip enable active low input. Connect CE = High to disable the IC and turn the input FET off. Connect CE = low for normal operation. CE is internally pulled down.             |  |  |

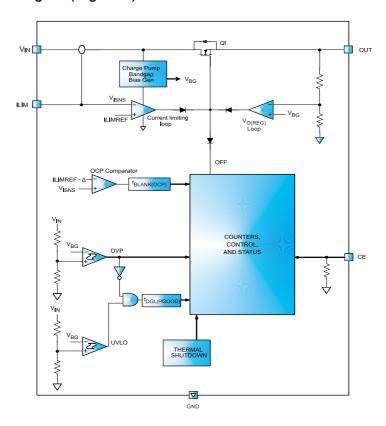

#### Simplified Block Diagram(Figure 1)

#### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER            | PIN                                                                    | VALUE                             | UNIT |  |

|------------------|----------------------|------------------------------------------------------------------------|-----------------------------------|------|--|

|                  |                      | IN (with respect to VSS)                                               | -0.3 to 30                        | V    |  |

| $V_{I}$          | Input voltage        | OUT (with respect to VSS)                                              | -0.3 to 7                         |      |  |

|                  |                      | ILIM, CE,                                                              | -0.3 to 7                         |      |  |

| l <sub>l</sub>   | Input current        | IN                                                                     | 2                                 | А    |  |

| lo               | Output current       | OUT                                                                    | 2                                 | А    |  |

|                  |                      | All (Human Body)                                                       | 2000                              | V    |  |

|                  |                      | All (Machine)                                                          | 200                               | V    |  |

| ESD              | Withstand Voltage    | All (Charge Device)                                                    | 500                               | V    |  |

|                  |                      | IN (with IN bypassed to the VSS with a 1-μF low-ESR ceramic capacitor) | 15 (Air Discharge)<br>8 (Contact) | kV   |  |

| TJ               | Junction temperature |                                                                        | -40 to 150                        | °C   |  |

| T <sub>stg</sub> | Storage temperature  |                                                                        | -65 to 150                        | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

#### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                     |                          | MIN             | MAX | UNIT |

|---------------------|--------------------------|-----------------|-----|------|

| V <sub>IN</sub>     | Input voltage range      | 3.3             | 30  | V    |

| I <sub>IN</sub>     | Input current, IN pin    |                 | 1.2 | Α    |

| I <sub>OUT</sub>    | Output current, OUT pin  |                 | 1.2 | Α    |

| R <sub>(ILIM)</sub> | OCP Programming resistor | 9               | 50  | kΩ   |

| TJ                  | Junction temperature     | <del>-4</del> 0 | 125 | °C   |

#### **Order Information**

| Device  | Package  | Making | Reel Size | Tape Width | Quantity |

|---------|----------|--------|-----------|------------|----------|

| CS5805S | SOT23-6L | FIAF X | 7"        | 8mm        | 3000     |

**ELECTRICAL CHARACTERISTICS** over junction temperature range –40°C to 125°C and recommended supply voltage (unless otherwise noted)

|                         | PARAMETER                                             | TEST CONDITIONS                                                                                                                 | MIN  | TYP  | MAX      | UNIT   |

|-------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|----------|--------|

| IN                      |                                                       |                                                                                                                                 |      |      |          |        |

| UVLO                    | Undervoltage lock-out, input power detected threshold | □ = Low, V <sub>IN</sub> increasing from 0V to 3V                                                                               | 2.6  | 2.7  | 2.8      | ٧      |

| V <sub>hys(UVLO)</sub>  | Hysteresis on UVLO                                    | CE = Low, V <sub>IN</sub> decreasing from 3V to 0V                                                                              | 160  | 200  | 240      | mV     |

| t <sub>DGL(PGOOD)</sub> | Deglitch time, input power detected status            | $\overline{CE}$ = Low. Time measured from $V_{IN}~0V \rightarrow 5V~1\mu s$ rise-time, to output turning ON                     |      | 16   |          | ms     |

| I <sub>DD</sub>         | Operating current                                     | $\overline{CE}$ = Low, No load on OUT pin,<br>V <sub>IN</sub> = 5V, R <sub>(ILIM)</sub> = 25k $\Omega$                          |      | 580  |          | μΑ     |

| I <sub>STDBY</sub>      | Standby current                                       | CE = High, V <sub>IN</sub> = 5V                                                                                                 |      | 75   | 95       | μΑ     |

| INPUT TO C              | OUTPUT CHARACTERISTICS                                |                                                                                                                                 |      |      |          |        |

| $V_{DO}$                | Drop-out voltage IN to OUT                            | $\overline{\text{CE}}$ = Low, V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 1A                                                       |      | 250  | 280      | mV     |

| r <sub>DS(on)</sub>     | Drain-sourceon-state resistance                       | CE = Low, V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 1A                                                                           |      | 0.24 |          | Ω      |

| OUPUT VOI               | TAGE REGULATION                                       |                                                                                                                                 |      |      |          |        |

| $V_{O(REG)}$            | Output voltage                                        | CE = Low, V <sub>IN</sub> = 5.7V, I <sub>OUT</sub> = No Load                                                                    |      | 5.45 | 5.60     | ٧      |

| INPUT OVE               | RVOLTAGE PROTECTION                                   |                                                                                                                                 |      |      |          |        |

| V <sub>OVP</sub>        | Input overvoltage protection threshold                | CE = Low, V <sub>IN</sub> increasing from 5V to 11V                                                                             | 5.85 | 6.1  | 6.4      | V      |

| t <sub>PD(OVP)</sub>    | Input OV propagation delay <sup>(1)</sup>             | CE = Low                                                                                                                        |      | 200  |          | ns     |

| $V_{hys(OVP)}$          | Hysteresis on OVP                                     | CE = Low, V <sub>IN</sub> decreasing from 11V to 5V                                                                             | 20   | 100  | 110      | mV     |

| t <sub>ON(OVP)</sub>    | Recovery time from input overvoltage condition        | $\overline{\text{CE}}$ = Low, Time measured from $V_{\text{IN}}$ 7.5V $\rightarrow$ 5V, 1 $\mu$ s fall-time                     |      | 16   |          | ms     |

| INPUT OVE               | RCURRENT PROTECTION                                   |                                                                                                                                 |      |      | <u>'</u> |        |

| I <sub>OCP</sub>        | Input overcurrent protection threshold range          |                                                                                                                                 | 300  |      | 1000     | mA     |

| I <sub>OCP</sub>        | Input overcurrent protection threshold                | $\overline{CE}$ = Low, R <sub>(ILIM)</sub> =15 k $\Omega$ ,<br>3 V ≤ V <sub>IN</sub> < V <sub>OVP</sub> - V <sub>hys(OVP)</sub> | 500  | 600  | 700      | mA     |

| K <sub>(ILIM)</sub>     | Adjustable current limit factor                       |                                                                                                                                 |      | 9    |          | A = kΩ |

| t <sub>BLANK(OCP)</sub> | Blanking time, input overcurrent detected             |                                                                                                                                 |      | 240  |          | μs     |

| t <sub>REC(OCP)</sub>   | Recovery time from input overcurrent condition        |                                                                                                                                 |      | 128  |          | ms     |

| THERMAL F               | PROTECTION                                            |                                                                                                                                 |      |      |          |        |

| T <sub>J(OFF)</sub>     | Thermal shutdown temperature                          |                                                                                                                                 |      | 140  | 150      | °C     |

| T <sub>J(OFF-HYS)</sub> | Thermal shutdown hysteresis                           |                                                                                                                                 |      | 20   |          | °C     |

| LOGIC LEV               | ELS ON CE                                             |                                                                                                                                 |      |      |          |        |

| $V_{IL}$                | Low-level input voltage                               |                                                                                                                                 | 0    |      | 0.4      | V      |

| $V_{IH}$                | High-level input voltage                              |                                                                                                                                 | 1.4  |      |          | V      |

| I <sub>IL</sub>         | Low-level input current                               | V <sub>(/CE)</sub> = 0V                                                                                                         |      |      | 1        | μΑ     |

| l <sub>IH</sub>         | High-level input current                              | V <sub>(/CE)</sub> = 1.8V                                                                                                       |      |      | 15       | μΑ     |

<sup>(1)</sup> Not tested in production. Specified by design.

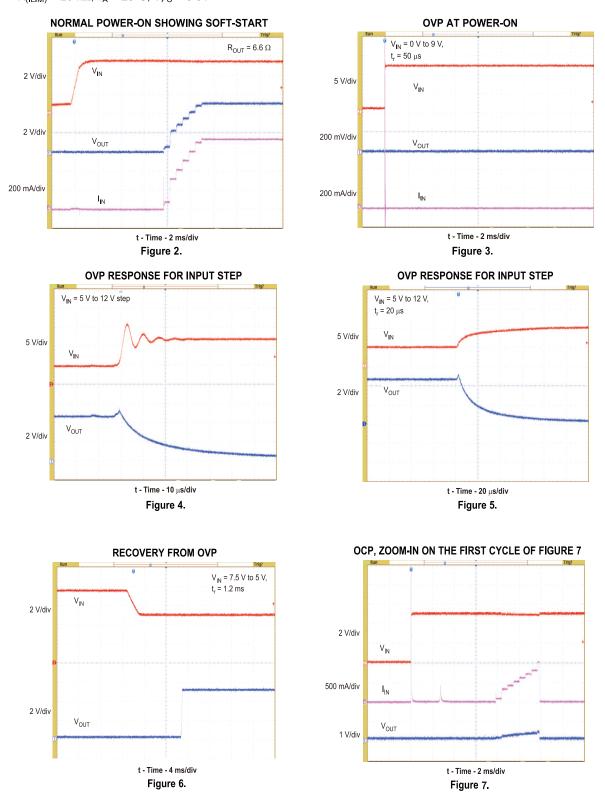

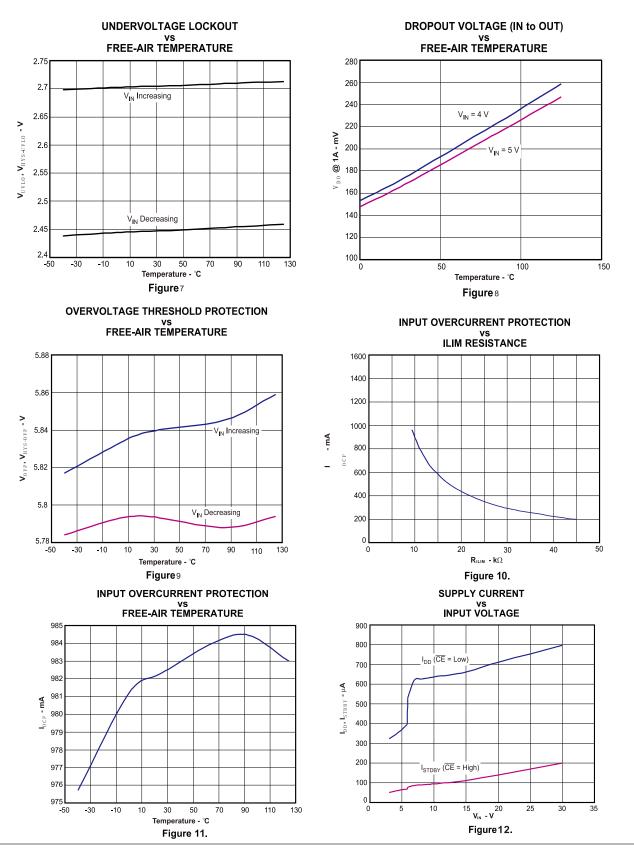

#### TYPICAL PERFORMANCE CHARACTERISTICS

Test conditions (unless otherwise noted) for typical operating performance:  $V_{IN}$  = 5 V,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F,  $C_{ILIM}$ ) = 25 k $\Omega$ ,  $T_A$  = 25°C,  $V_{PU}$  = 3.3V

#### **TYPICAL OPERATING PERFORMANCE (continued)**

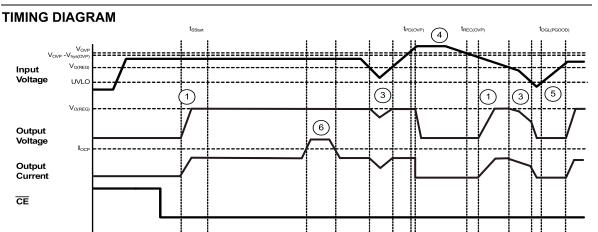

- 1. Normal start-up condition

- 2. V UVLO < VIN < VO(REG), VOUT tracks VIN

- Input over-voltage event

- Input below UVLO

- 5. High-current event during normal operation

#### **DETAILED FUNCTIONAL DESCRIPTION**

CS5805S is a integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage. For an input overvoltage condition, the IC immediately removes power from the charging circuit by turning off an internal switch. For an overcurrent condition, it limits the system current at the threshold value, and if the overcurrent persists, switches the pass element OFF after a blanking period. Additionally, the IC also monitors its own die temperature and switches off if it exceeds 140°C. The input overcurrent threshold is user-programmable. The IC can be controlled by a processor.

#### **POWER DOWN**

The device remains in power down mode when the input voltage at the IN pin is below the undervoltage threshold UVLO. The FET Q1 connected between IN and OUT pins is off.

#### **POWER-ON RESET**

The device resets when the input voltage at the IN pin exceeds the UVLO threshold. All internal counters and other circuit blocks are reset. The IC then waits for duration  $t_{\tiny DGL(PGOOD)}$  for the input voltage to stabilize. FET Q1 is turned ON. The IC has a soft-start feature to control the inrush current. The soft-start minimizes the ringing at the input (the ringing occurs because the parasitic inductance of the adapter cable and the input bypass capacitor form a resonant circuit). Because of the deglitch time at power-on, if the input voltage rises rapidly to beyond the OVP threshold, the device will not switch on at all, instead it will go into protection mode .

#### **OPERATION**

The device continuously monitors the input voltage, the input currentas described in detail in the following sections.

#### Input Overvoltage Protection

While the input voltage is less than  $V_{\text{O(REG)}}$ , the output voltage tracks the input voltage (less the drop due to the  $R_{\text{DS(on)}}$  of Q1). When the input voltage is between  $V_{\text{O(REG)}}$  and  $V_{\text{OVP}}$ , the device functions as a linear regulator and regulates the output voltage to 5.15V. If the input voltage rises above  $V_{\text{OVP}}$ , the internal FET Q1 is turned off, removing power to the output. The response is rapid, with the FET turning off in less than a

#### **Input Overcurrent Protection**

The overcurrent threshold is programmed by a resistor  $R_{\mbox{\tiny (ILIM)}}$  connected from the ILIM pin to VSS. Figure 10 shows the OCP threshold as a function of R<sub>(ILIM)</sub>, and may be approximated by the following equation:  $I_{OCP} = 9 \div R_{(ILIM)}$  (current in A, resistance in  $k\Omega)$  If the load current tries to exceed the I<sub>OCP</sub> threshold, the device limits the current for a blanking duration of  $t_{\text{\tiny BLANK(OCP)}}$ . If the load current returns to less than  $\rm I_{\rm OCP}$  before  $\rm t_{\rm BLANK(OCP)}$  times out, the device continues to operate. However, if the overcurrent situation persists for  $t_{\mbox{\tiny BLANK(OCP)}}$ , the FET Q1 is turned off for a duration of  $t_{\text{REC(OCP)}}$  . The FET is then turned on again after  $t_{\mbox{\tiny REC(OCP)}}$  and the current is monitored all over again. To prevent the input voltage from spiking up due to the inductance of the input cable, Q1 is turned off slowly, resulting in a "soft-stop".

#### **Thermal Protection**

If the junction temperature of the device exceeds  $T_{\text{J(OFF)}}$ , the FET Q1 is turned off. The FET is turned back on when the junction temperature falls below  $T_{\text{J(OFF)}}$ –  $T_{\text{J(OFF-HYS)}}$ .

#### **Enable Function**

The IC has an enable pin which can be used to enable or disable the device. When the CE pin is driven high, the internal FET is turned off. When the CE pin is low, the FET is turned on if other conditions are safe. The CE pin has an internal pulldown resistor and can be left floating.

# APPLICATION INFORMATION (WITH REFERENCE TO FIGURE a) Selection of $R_{\rm ce}$

The CE pin can be used to enable and disable the IC. If host control is not required, the CE pin can be tied to ground or left un-connected, permanently enabling the device.

In applications where external control is required, the CE pin can be controlled by a host processor. the CE pin should be connected to the host GPIO pin through as large a resistor as possible. The limitation on the resistor value is that the minimum  $V_{\text{OH}}$  of the host GPIO pin less the drop across the resistor should be greater than  $V_{\text{IH}}$  of the CS5805S CE pin. The drop across the resistor is given by  $R_{\text{CE}} \times I_{\text{IH}}.$

## Selection of Input and Output Bypass Capacitors

The input capacitor C<sub>IN</sub> in Figure a is for decoupling, and serves an important purpose. Whenever there is a step change downwards in the system load current, the inductance of the input cable causes the input voltage to C<sub>IN</sub> prevents the input voltage from overshooting to dangerous levels. It is recommended that a ceramic capacitor of at least 1µF be used at the input of the device. It should be located in close proximity to the IN pin.C<sub>out</sub> in Figure a is also important: If a fast (< 1µs rise time) overvoltage transient occurs at the input, the current that charges  $C_{\text{out}}$  causes the device's currentlimiting loop to start, reducing the gate-drive to FET Q1. This results in improved performance for input overvoltage protection.  $C_{\text{out}}$  should also be a ceramic capacitor of at least 1µF, located close to the OUT pin. C<sub>out</sub> also serves as the input decoupling capacitor for the charging circuit downstream of the protection IC.

#### **Powering Accessories**

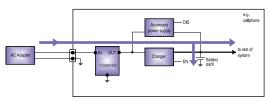

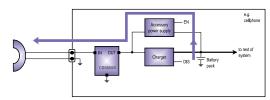

In some applications, the equipment that the protection IC resides in may be required to provide power to an accessory (e.g. a cellphone may power a headset or an external memory card) through the same connector pins that are used by the adapter for charging. Figure 13 and Figure 14 illustrate typical charging and accessory-powering scenarios:

Figure 13 . Charging - The Red Arrows Show the Direction of Current Flow

Figure 14 . Powering an Accessory - The Red Arrows Show the Direction of Current Flow

In the second case, when power is being delivered to an accessory, the CS5805S device is required to support current flow from the OUT pin to the IN pin. If  $V_{\text{OUT}} > \text{UVLO} + 0.7\text{V}$ , FET Q1 is turned on, and the reverse current does not flow through the diode but through Q1. Q1 remains ON as long as  $V_{\text{OUT}} > \text{UVLO} - V_{\text{hys(UVLO)}} + R_{\text{DS(on)}} \times I_{\text{(ACCESSORY)}}$ . Within this voltage range, the reverse current capability is the same as the forward capability, 1.0A. It should be noted that there is no overcurrent protection in this direction.

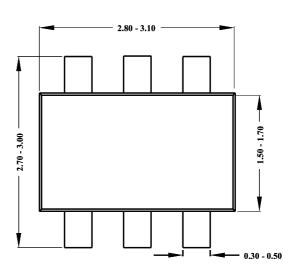

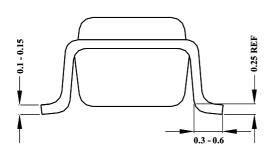

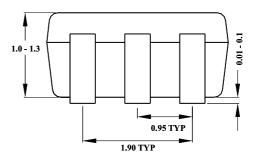

#### **PACKAGE INFORMATION**

SOT23-6L Package Outline & PCB Layout

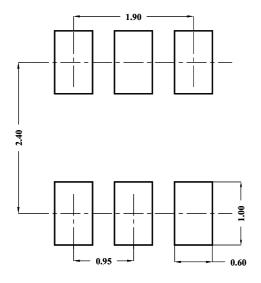

### **Recommended Pad Layout**

**Top View**

Notes: All dimension in MM

All dimension don't not include mold flash & metal burr