# 130mW, Differential Input DirectDrive Headphone Amplifiers

## **General Description**

The CS4418D stereo headphone driver is designed for portable equipment where board space is at a premium. The CS4418D uses a unique DirectDrive

architecture to produce a ground-referenced output

from a single supply, eliminating the need for large DC-locking capacitors, saving cost, board space, and component height. The CS4418D delivers up to 130mW per channel into a  $16\Omega$  load and has low 0.006% THD + N. A high powersupply rejection ratio 86dB at 1kHz) allows this device to operate from noisy digital supplies without an additional linear regulator. Comprehensive clickand-pop circuitry suppresses audible clicks and pops on startup and shutdown. Independent left/right, low-power shutdown controls make it possible to optimize power savings in mixed mode, mono/stereo applications.

The CS4418D operates from a single 1.8V to 5.5V supply, consumes only 5mA of supply current, has short-circuit and thermal overload protection, and is specified over the extended  $-20^{\circ}$ C.

CS4418D is available in a tiny 16-pin QFN3X3 package.

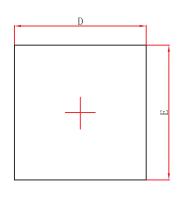

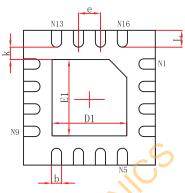

# Package

QFN3X3\_16L

#### **Features**

- No Bulky DC-Blocking Capacitors Required

- Ground-Referenced Outputs Eliminate DC-Bias Voltages on Headphone Ground Pin

- No Degradation of Low-Frequency Response Due to Output Capacitors

- 130mW Per Channel into  $16\Omega$

- Low 0.006% THD + N

- High PSRR (86dB at 1kHz)

- Integrated Click-and-Pop Suppression

- 1.8V to 5.5V Single-Supply Operation

- Low Quiescent Current

- Independent Left/Right, Low-Power Shutdown Controls

- Short-Circuit and Thermal Overload Protection

## **Applications**

- Notebooks

- Cellular Phones

- PDAs

- MP3 Players

- Web Pads

- Portable Audio Equipment

# **Pin Description**

| Pin No. | NAME  | 1/0        | Function                                                                 |

|---------|-------|------------|--------------------------------------------------------------------------|

| 1       | PVDD  | Р          | Charge-Pump Power Supply.                                                |

| 2       | СР    |            | Flying Capacitor Positive Terminal                                       |

| 3       | PGND  | GND        | Power Ground. Connect to SGND.                                           |

| 4       | CN    | _          | Flying Capacitor Negative Terminal                                       |

| 5       | PVSS  | Р          | Charge-Pump Negative Supply Output                                       |

| 6       | INPL  | -          | Positive audio Input for Left-Channel Audio                              |

| 7       | INNL  | 1          | Negative audio Input for Left-Channel Audio                              |

| 8       | OUTL  | 0          | Left-Channel Output                                                      |

| 9       | PVDD  | Р          | Charge-Pump Power Supply.                                                |

| 10      | PVSS  | Р          | Charge-Pump Negative Supply Output                                       |

| 11      | OUTR  | 0          | Right-Channel Output                                                     |

| 12      | SHDNR | Ι          | Active-Low, Right-Channel Shutdown. Connect to VDD for normal operation. |

| 13      | INNR  | <u>_</u> , | Negative audio Input for Right-Channel Audio                             |

| 14      | INPR  | I          | Positive audio Input for Right-Channel Audio                             |

| 15      | SGND  | GND        | Signal Ground. Connect to PGND.                                          |

| 16      | SHDNL | I          | Active-Low, Left-Channel Shutdown. Connect to VDD for normal operation.  |

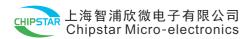

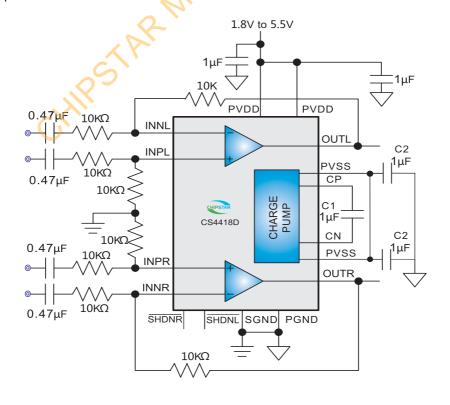

# **Typical Application**

# Absolute Maximum Ratings 1

| Symbol           | Description                                     | Value           | Unit |

|------------------|-------------------------------------------------|-----------------|------|

| $V_{DD}$         | Supply Voltage at no Input Signal               | 6               | V    |

| V <sub>I</sub>   | Input Voltage                                   | -0.3 to VDD+0.3 | V    |

| T <sub>J</sub>   | Operating Junction Temperature Range            | -40 to 150      | °C   |

| T <sub>SDR</sub> | Maximum Lead Soldering Temperature , 10 Seconds | 300             | °C   |

| T <sub>STG</sub> | Storage Temperature Range                       | -65 to 150      | °C   |

# **Recommended Operating Conditions**

| Symbol          | Description                | Value   | Unit |

|-----------------|----------------------------|---------|------|

| V <sub>DD</sub> | Supply Voltage             | 1.8~5.5 | V    |

| TA              | Ambient Temperature Range  | -40~85  | °C   |

| TJ              | Junction Temperature Range | -40~125 | °C   |

# Thermal Information <sup>2</sup>

| Symbol          | Description                            |   | Value | Unit |

|-----------------|----------------------------------------|---|-------|------|

| $\theta_{JA}$   | Thermal Resistance-Junction to Ambient | U | 160   | °C/W |

| θ <sub>JC</sub> | Thermal Resistance-Junction to Case    |   | 56    | °C/W |

# **Ordering and Marking Information**

| Device  | Package Type | Device Marking                                                    | Reel Size | Tape Width | Quantity   |

|---------|--------------|-------------------------------------------------------------------|-----------|------------|------------|

| CS4418D | QFN3X3_16L   | ○ 12 12 12<br>24 7 - 17<br>25 00 00 00 17<br>27 1 17<br>27 1 2 17 | 13"       | 12mm       | 3000 units |

# ESD Susceptibility

| ESD Susceptibility-HBM | <del></del> | ±6kV  |

|------------------------|-------------|-------|

| ESD Susceptibility-MM  |             | ±200V |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at one time.

### **ELECTRICAL CHARACTERISTICS**

$(PV_{\tiny DD} = SV_{\tiny DD} = 3V, PGND = SGND = 0V, SHDNL = SHDNR = SV_{\tiny DD}, C1 = C2 = 1\mu F, C_{\tiny IN} = 1\mu F, R_{\tiny L} = \ \ , T_{\tiny A} = T_{\tiny MIN} to \ T_{\tiny MAX}, unless otherwise noted. Typical values are at T_{\tiny A} = +25^{\circ}C.)$

| PARAMETER                      | SYMBOL                      | CONDI <sup>*</sup>                                | TIONS                   | MIN | TYP   | MAX  | UNITS  |  |

|--------------------------------|-----------------------------|---------------------------------------------------|-------------------------|-----|-------|------|--------|--|

| Supply Voltage Range           | VDD                         | Guaranteed by PS                                  | 1.8                     | 3.0 | 5.5   | V    |        |  |

| Quiescent Supply Current       | Inn                         | One channel enabled                               |                         |     | 3.3   |      | mA     |  |

| Quiescent supply current       | IDD                         | Two channel enab                                  | led                     | 4   |       |      |        |  |

| Shutdown Supply Current        | ISHDN                       | SHDNL=SHDNR=                                      | :GND                    |     | 0.02  |      | μΑ     |  |

| OLIDAL Througholds             |                             | VIH                                               |                         | 1.4 |       |      | V      |  |

| SHDN_ Thresholds               |                             | VIL                                               |                         |     |       | 0.4  | V<br>I |  |

| SHDN_Input Leakage Current     |                             |                                                   |                         | -1  |       | +1   | μΑ     |  |

| SHDN_to Full Operation         | tson                        |                                                   |                         |     | 36    | )    | ms     |  |

| CHARGE PUMP                    |                             |                                                   |                         |     | 710   |      |        |  |

| Oscillator Frequency           | fosc                        |                                                   |                         | 400 | 500   | 600  | kHz    |  |

| AMPLIFIERS                     |                             |                                                   |                         | .0  |       |      |        |  |

| Input Offset Voltage           | Vos                         | Input AC-coupled,                                 | $R_L = 32\Omega$        |     | 100   |      | μV     |  |

| Power-Supply Rejection         | PSRR                        | 1.8V ≤V <sub>DD</sub> ≤5.5V                       | Dc                      | 75  | 90    |      |        |  |

| Ratio                          |                             | 200mVp-p ripple                                   | fRIPPLE = 1kHz          |     | 90    |      | dB     |  |

|                                |                             |                                                   | fRIPPLE = 20kHz         |     | 55    |      | ub_    |  |

| Output Power                   | Роит                        | Pout THD + N = 1%                                 | $R_L = 32\Omega$        | 24  | 90    | 260  | mW     |  |

| Output i ower                  |                             |                                                   | $R_{\rm L} = 16\Omega$  | 25  | 97    | 300  |        |  |

| Total Harmonic Distortion Plus | THD + N fin:                |                                                   | RL = 32Ω<br>Pout = 25mW |     | 0.005 |      | %      |  |

| Noise                          |                             | fin= 1kHz                                         | R = 16Ω<br>Pout = 50mW  |     |       |      |        |  |

| Signal-to-Noise Ratio          | SNR                         | RL = 32Ω, Pout = 20mW, fIN = 1kHz                 |                         |     | 99    |      | dB     |  |

| Slew Rate                      | SR                          |                                                   |                         | 0.8 |       | V/µs |        |  |

| Maximum Capacitive Load        | CL                          | No sustained oscillations                         |                         |     | 300   |      | рF     |  |

| Crosstalk                      | N.                          | RL = $16\Omega$ , Pout = $1.6$ mW, fIN = $10$ kHz |                         |     | 70    |      | dB     |  |

| Thermal Shutdown Threshold     | hermal Shutdown Threshold   |                                                   |                         | 140 |       | °C   |        |  |

| Thermal Shutdown Hysteresis    | Thermal Shutdown Hysteresis |                                                   |                         |     | 15    |      | °C     |  |

Note: All specifications are 100% tested at TA = +25°C; temperature limits are guaranteed by design.

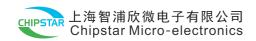

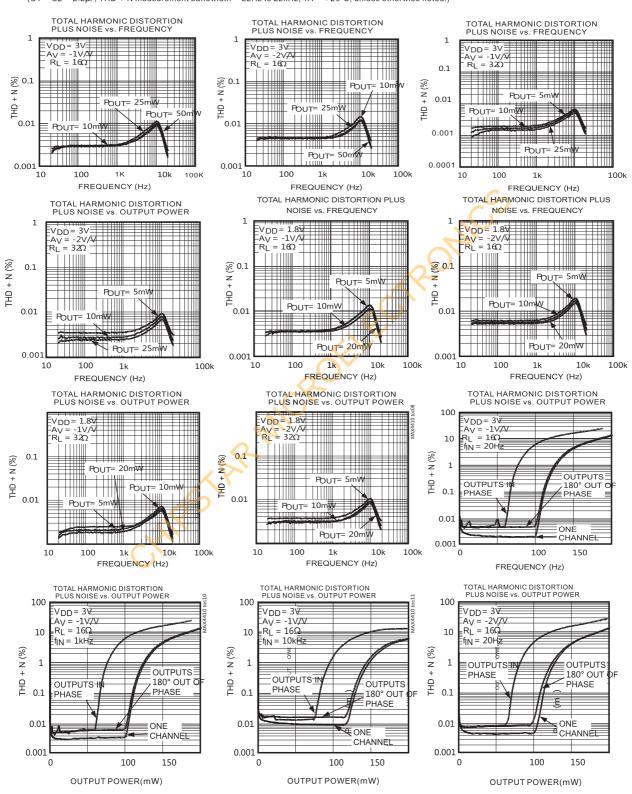

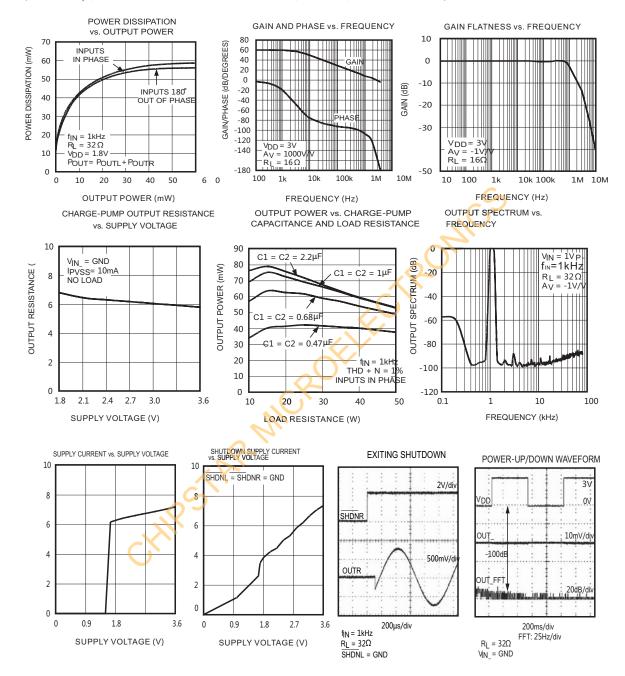

#### **Typical Operating Characteristics**

(C1 = C2 =  $2.2\mu F$ , THD + N measurement bandwidth = 22Hz to 22kHz, TA =  $+25^{\circ}C$ , unless otherwise noted.)

#### **Typical Operating Characteristics** (C1 = C2 = $2.2\mu F$ , THD + N measurement bandwidth = 22Hz to 22kHz, TA = $+25^{\circ}C$ , unless otherwise noted.) TOTAL HARMONIC DISTORTION TOTAL HARMONIC DISTORTION TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER PLUS NOISE vs. OUTPUT POWER 100 100 100 V<sub>DD</sub>= 3₩ V<sub>DD</sub>= 3∀ V<sub>DD</sub>= 3\ -2V/V -2VZV $A_V = -1V_7$ $R_1 = 320^{\circ}$ -1V - -∠ν RĽ = 16Ω - 160 10 10 $f_{|N} = 1kHz$ f<sub>IN</sub> = 10kHz $f_{\rm IN} = 20H_{\rm Z}$ (%) N + (%) N + (%) N + QHJ 1 OUTPUTS OUTPUTS CHANNE PHASE 0.1 180° OUT PHASE OUTPUITS 모 모 PHASE 180° OUT 0.1 0.1 OUTPUTS 180° OUT PHASE 0.01 PHASE 0.01 0.01 ONF 0.001 CHANNEL CHANNET 0.001 0.001 0.0001 200 50 200 0 50 100 150 0 100 150 0 5.0 7 5 100 125 OUTPUT POWER (mW) OUTPUT POWER (mW) OUTPUT POWER (mW) TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER 100 100 /DD= 3₹ V<sub>DD</sub>= 3√ Av = -1√/ V<sub>DD</sub>= 3√ -1VZV -1\//\/ AV = -1V/ $RL = 32\Omega$ $R_L = 32\Omega_{\perp}$ $f_{|N} = 1kHz$ = 32Ω 10 10 f<sub>IN</sub> = 20Hz f<sub>IN</sub> = 10kHz (%) N + 8 (%) N + QH1 1 1 1 OUTPUT 몬 모 OUTPUTS OUTPUTS 180° OUT PHASE 0.1 0.1 0.1 180° OUT 180° OUT € ONE PHASE PHASE ONE CHANNE ONE CHANN 0.01 CHAN 0.01 0.01 0.001 0.001 0.001 25 0 25 50 75 100 125 0 50 75 100 125 0 50 75 100 **OUTPUT POWER (mW)** OUTPUT POWER (mW) TOTAL HARMONIC DISTORTION TOTAL HARMONIC DISTORTION TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER PLUS NOISE vs. OUTPUT POWER PLUS NOISE vs. OUTPUT POWER 100 100 100 $V_{DD} = 3V$ $A_V = -2V_IV$ $R_L = 32\Omega$ $f_{IN} = 10kHz$ V<sub>DD</sub>= 1.8∀ Vnn= 3₹ $A_V = -2V_L$ $R_L = 32\Omega_L$ $f_{|N} = 1kH_Z$ AV = -1V/V AV = -1V/V $RL = 16\Omega$ $f_{|N} = 20H$ -2V/V 10 10 10 (%) N + (%) N + 8 1 1 Z + OUTPUTS 문 OUTPUTS 모 180° OUT OF OUTPUTS 0.1 ONE 0.1 0.1 OUT 180 PHASE OUT 180 PHASE ONE -PHASE 0.01 0.01 0.01 ONE CHANNE 0.001 0.001 0.001 0 50 100 10 2 0 30 OUTPUT POWER (mW) OUTPUT POWER (mW) OUTPUT POWER (mW) TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER TOTAL HARMONIC DISTORTION TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER PLUS NOISE vs. OUTPUT POWER 100 100 100 V<sub>DD</sub> = 1.<del>8∀</del> V<sub>DD</sub>= 1.<del>8∀</del> V<sub>DD</sub>= 1.<del>8∀</del> $A_V = -1V/V$ $R_L = 16\Omega$ $A_V = -2V/V$ $R_L = 16\Omega$ = -1V/V $R_i = 16\Omega$ 10 10 10 fin = 1kHz f<sub>IN</sub> = 10k f<sub>IN</sub> = 20H<del>z</del> (%) N (%) N % N 1 1 1

문

0.1

0.01

0.001

0

OUTPUT POWER (mW)

2.0 30

OUTPUTS

180° OUT

PHASE

ONE CHANNE

4 0

5 600

OUTPUTS IN

PHASE

모

180° OUT **Œ**

PHASE

CHANNE

4 0

5 0

ONE

2 0 30

OUTPUT POWER (mW)

0.1

0.01

0.001

0 10 5600

OUTPUTS

PHASE

CHANNE

ONE

2180° OUT €

OUTPUTS

2 0

OUTPUT POWER (mW)

PHASE

모

0.1

0.01

0.001

0

#### **Typical Operating Characteristics** (C1 = C2 = $2.2\mu F$ , THD + N measurement bandwidth = 22Hz to 22kHz, TA = $+25^{\circ}C$ , unless otherwise noted.) TOTAL HARMONIC DISTORTION TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER PLUS NOISE vs. OUTPUT POWER 100 100 100 V<sub>DD</sub>= 1.8<del>V</del> A<sub>V</sub> = -2V/V R<sub>L</sub> = 16Ω V<sub>DD</sub>= 1.8₩ $V_{DD} = 1.8$ $A_V = -1$ $A_L = 32$ $A_{DD} = 20$ AV = -2V/V $AV = 16\Omega$ $f_{|N} = 10k$ 10 10 10 fin = 1kHz (%) N + (%) N + THD + N (%) 1 1 OUTPUTS# PHASE PHASE 문 OUTPUTS 180° OUT 모 OUTPUTS 0.1 0.1 0.1 180° OUT **≥** 180° OUT **€** PHASE PHASE PHASE 0.01 ONE 0.01 0.01 CHANNE CHANNET CHANNEL 0.001 0.001 0.001 2 0 30 4 0 10 2 0 30 4 0 30 4 0 5 0 OUTPUT POWER (mW) OUTPUT POWER (mW) OUTPUT POWER (mW) TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER 100 100 100 $V_{DD} = 1.8V$ AV = -1V/V $RL = 32\Omega$ $f_{IN} = 10kHz$ $V_{DD} = 1.8$ $A_V = -2$ $V_{DD} = 1.8$ $A_V = -2$ $V_{DD} = 1.8$ $A_V = -1$ $V_{DD} = 1.8$ $V_{DD} = 1.8$ $V_{DD} = 1.8$ $V_{DD} = 1.8$ 1.8∀ 10 10 10 f<sub>IN</sub> = 20Hz % 1 + OHL 0.1 %) N 1 + OHL 0.1 (%) N + OUTPUTS IN 1 PHASE OUTPUTS OUTPUTS# OUTPUTS∓ OUTPUTS 180° OUT PHASE OUTPUTS = 180° OUT OF 180° OUT OF PHASE 문 PHASE PHASE 0.1 PHASE 0.01 0.01 0.01 CHANNE CHANNE 0.001 0.001 5 0 0.001 2 0 30 4 0 2 0 30 4 0 5 0 5 0 OUTPUT POWER (mW) OUTPUT POWER (mW) **OUTPUT POWER (mW)** TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER POWER-SUPPLY REJECTION RATIO vs. FREQUENCY 100 100 V<sub>DD</sub> = 1.8<del>V</del> A<sub>V</sub> = -2V/V R<sub>L</sub> = 32Ω V<sub>DD</sub> = 3V R<sub>I</sub> = 16Ω V<sub>DD</sub> = 1.8<del>V</del> A<sub>V</sub> = -2V/V -20 10 10 $= 32\Omega$ f<sub>IN</sub> = 10kHz $f_{|N} = 1kHz$ (%) N + (%) N + OUTPUTS B -40 1 1 PHASE OUTPUTS IN PSRR R 180° OUT OUTPUTS PHASE <sup>무</sup> 0.1 문 180° OUT OF 0.1 CHANNEL -80 0.01 ONE 0.01 0.001 0.001 -100 0.01 0.1 10 4 0 5 0 0 10 2.0 30 4 0 5.0 0 10 2 0 30 FREQUENCY (kHz) OUTPUT POWER (mW) OUTPUT POWER (mW) POWER-SUPPLY REJECTION RATIO vs. FREQUENCY POWER-SUPPLY REJECTION RATIO vs. FREQUENCY POWER-SUPPLY REJECTION RATIO vs. FREQUENCY V<sub>DD</sub> = 1.8V R<sub>L</sub> = 16Ω V<sub>DD</sub> = 3V R<sub>L</sub> = 32Ω V<sub>DD</sub> = 1.8\ R<sub>L</sub> = 32Ω -20 -20 -20 <mark>-40</mark> 원 -40 -40 PSRR PSRR PSRR -60 -60 -80 -80 -80 -100 -100 -100 0.01 100 0.01 0.1 10 100 0.1 10 0.01 0.1 10 100

FREQUENCY (kHz)

FREQUENCY (kHz)

FREQUENCY (kHz)

#### **Typical Operating Characteristics**

(C1 = C2 =  $2.2\mu F$ , THD + N measurement bandwidth = 22Hz to 22kHz, TA =  $+25^{\circ}C$ , unless otherwise noted.)

#### **Typical Operating Characteristics**

(C1 = C2 =  $2.2\mu F$ , THD + N measurement bandwidth = 22Hz to 22kHz, TA =  $+25^{\circ}C$ , unless otherwise noted.)

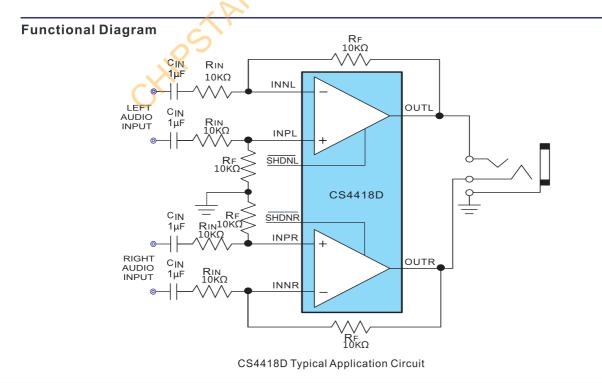

#### **Detailed Description**

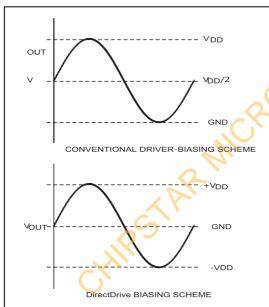

The CS4418D stereo headphone driver features DirectDrive architecture, eliminating the large outputcoupling capacitors required by traditional single-supply headphone drivers. The device consists of two 130mW ClassAB headphone drivers, undervoltage lockout (UVLO)/shutdown control, charge-pump, and comprehensive click-and-pop suppression circuitry (see Typical Application Circuit). The charge pump inverts the positive supply (PVDD), creating a negative supply (PVSS). The headphone drivers operate from these bipolar supplies with their outputs biased about GND (Figure 1). The drivers have almost twice the supply range compared to other 3V single-supply drivers, increasing the available

output power. The benefit of this GND bias is that the driver outputs do not have a DC component typically VDD/2. Thus, the large DC-blocking capacitors are unnecessary, improving frequency response while conserving board space and system cost.

Each channel has independent left/right, active-low shutdown controls, making it possible to optimize power savings in mixed-mode, mono/stereo operation. The device features an undervoltage lockout that prevents operation from an insufficient power supply and click-and-pop suppression that eliminates audible transients on startup and shutdown. Additionally, the CS4418D features thermal overload and short-circuit protection

Figure 1. Traditional Driver Output Waveform vs. CS4418D Output Waveform

#### DirectDrive

www.chipstar-ic.com

Traditional single-supply headphone drivers have their outputs biased about a nominal DC voltage (typically half the supply) for maximum dynamic range. Large coupling capacitors are needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone driver. DirectDrive architecture uses a charge pump to create an internal negative supply voltage. This allows the outputs of the CS4418D to be biased about GND, almost doubling dynamic range while operating from a single supply. With no DC component, there is no need for the large DC-blocking capacitors. Instead of two large (220µF, typ) tantalum capacitors, the CS4418D charge pump requires two small ceramic capacitors, conserving board space, reducing cost, and improving the frequency response of the headphone driver. See the Output Power vs Charge-Pump Capacitance and Load Resistance graph in the Typical Operating Characteristics for details of the possible

capacitor sizes. There is a low DC voltage on the driver outputs due to amplifier offset. However, the offset of the CS4418D is typically 0.5mV, which, when combined with a  $32\Omega$  load, results in less than  $32\mu A$  of DC current flow to the headphones.

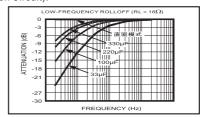

#### Low-Frequency Response

In addition to the cost and size disadvantages of the Dcblocking capacitors required by conventional headphone amplifiers, these capacitors limit the amplifier's low-frequency response and can distort the audio signal.

1) The impedance of the headphone load and the Dcblocking capacitor form a highpass filter with the -3dB point set by:

$$f$$

-3dB =  $\frac{1}{2\pi R_L C_{OUT}}$

where RL is the headphone impedance and COUT is the DC-blocking capacitor value. The highpass filter is required by conventional single-ended, single power-supply headphone drivers to block the midrail DC bias component of the audio signal from the headphones. The drawback to the filter is that it can attenuate low-frequency signals. Larger values of COUT reduce this effect but result in physically larger, more expensive capacitors. Figure 2 shows the relationship between the size of COUT and the resulting low-frequency attenuation. Note that the -3dB point for a  $16\Omega$  headphone with a  $100\mu\text{F}$  blocking capacitor is 100Hz, well within the normal audio band, resulting in low-frequency attenuation of the reproduced signal.

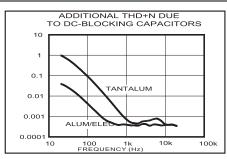

2) The voltage coefficient of the DC-blocking capacitor contributes distortion to the reproduced audio signal as the capacitance value varies as a function of the voltage change across the capacitor. At low frequencies, the reactance of the capacitor dominates at frequencies below the -3dB point and the voltage coefficient appears as frequency-dependent distortion. Figure 3 shows the THD + N introduced by two different capacitor dielectric types. Note that below 100Hz, THD + N increases rapidly. The combination of low-frequency attenuation and frequencydependent distortion compromises audio reproduction in portable audio equipment that emphasizes low-frequency effects such as multimedia laptops, as well as MP3, CD, and DVD players. By eliminating the DC-blocking capacitors through DirectDrive technology, these capacitor-related deficiencies are eliminated. The CS4418D features a low-noise charge pump. The 320kHz switching frequency is well beyond the audio range, and thus does not interfere with the audio signals. The switch drivers feature a controlled switching

speed that minimizes noise generated by turn-on and turnoff transients. By limiting the switching speed of the switches, the di/dt noise caused by the parasitic bond wire and trace inductance is minimized. Although not typically required, additional high-frequency noise attenuation can be achieved by increasing the size of C2 (see Typical Application Circuit).

Figure 2. Low-Frequency Attenuation for Common DC-Blocking Capacitor Values

Figure 3. Distortion Contributed by DC-Blocking Capacitors

#### Charge-Pump Capacitor Selection

Use capacitors with an ESR less than  $100m\Omega$  for optimum performance. Low-ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric.

#### Shutdown

The CS4418D features two shutdown controls allowing either channel to be shut down or muted independently.  $\overline{SHDNL}$  controls the left channel while  $\overline{SHDNR}$  controls the right channel. Driving either  $\overline{SHDN}$  low disables the respective channel, sets the driver output impedance to about  $1k\Omega$ , and reduces the supply current to less than  $10\mu$  A. When both  $\overline{SHDN}$  inputs are driven low, the charge pump is also disabled, further reducing supply current draw to  $6\mu$ A. The charge pump is enabled once either  $\overline{SHDN}$  input is driven high.

#### **Power Dissipation**

Under normal operating conditions, linear power amplifiers can dissipate a significant amount of power. The maximum power dissipation for each package is given in the Absolute Maximum Ratings section under Continuous Power Dissipation or can be calculated by the following equation:

$$P_{DISSPKG(MAX)} = \frac{T_J (MAX) - T_A}{\theta_{JA}}$$

where TJ(MAX) is +150°C, TA is the ambient temperature, and  $\theta$ JA is the reciprocal of the derating factor in °C/W as specified in the Absolute Maximum Ratings section. For example,  $\theta$  JA of the TSSOP package is +109.9°C/W.

The CS4418D has two sources of power dissipation, the charge pump and the two drivers. If the power dissipation for a given application exceeds the maximum allowed for a given package, either reduce VDD, increase load impedance, decrease the ambient temperature, or add heat sinking to the device. Large output, supply, and ground traces improve the maximum

power dissipation in the package. Thermal overload protection limits total power dissipation in the CS4418D. When the junction temperatureexceeds +140° C, the thermal protection circuitry disables the amplifier output stage. The amplifiers areenabled once the junction temperature cools by 15° C.This results in a pulsing output under continuous thermal overload conditions.

#### **Output Power**

The device has been specified for the worst-case scenario—when both inputs are in phase. Under this condition, the drivers simultaneously draw current from the charge pump, leading to a slight loss in headroom of VSS. In typical stereo audio applications, the left and right signals have differences in both magnitude and phase, subsequently leading to an increase in the maximum attainable output power.

#### Powering Other Circuits from a Negative Supply

An additional benefit of the CS4418D is the internally generated, negative supply voltage (-VDD). This voltage is used by the CS4418D to provide the ground-referenced output level. It can, however, also be used to power other devices within a design. Current draw from this negative supply (PVSS) should be limited to 5mA, exceeding this will affect the operation of the headphone driver. The negative supply voltage appears on the PVSS pin. A typical application is a negative supply to adjust the contrast of LCD modules. When considering the use of PVSS in this manner, note that the charge-pump voltage at PVSS is roughly proportional to -VDD and is not a regulated voltage. Thecharge-pump output impedance plot appears in the Typical Operating Characteristics.

#### Compensation Capacitor

The stability of the CS4418D is affected by the value of the feedback resistor (RF). The combination of RF and the input and parasitic trace capacitance introduces an additional pole. Adding a capacitor in parallel with RF compensates for this pole. Under typical conditions with proper layout, the device is stable without the additional capacitor.

#### Input Filtering

The input capacitor (Cin), in conjunction with RIN, forms a highpass filter that removes the DC bias from an incoming signal (see Typical Application Circuit). The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f$$

-3dB =  $\frac{1}{2\pi R_{IN}C_{IN}}$

Choose RIN according to the Gain-Setting Resistors section. Choose the CIN such that f-3dB is well below the lowest frequency of interest. Setting f-3dB too high affects the lowfrequency response of the amplifier. Use capacitors whose dielectrics have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, may result in increased distortion at low frequencies. Other considerations when designing the input filter include the constraints of the overall system and the actual frequency band of interest. Although high-fidelity audio calls for a flat-gain response between 20Hz and 20kHz, portable voice-reproduction devices such as cellular phones and two-way radios need only concentrate on the frequency range of the spoken human voice (typically 300Hz to 3.5kHz). In addition, speakers used in portable devices typically have a poor response below 150Hz. Taking these two factors into consideration, the input filter may not need to be designed for a 20Hz to 20kHz response, saving both board space and cost due to the use of smaller capacitors.

#### Flying Capacitor (C1)

The value of the flying capacitor (C1) affects the load regulation and output resistance of the charge pump. A C1 value that is too small degrades the device's ability to provide sufficient current drive, which leads to a loss of output voltage. Increasing the value of C1 improves load regulation and reduces the charge-pump output resistance to an extent. See the Output Power vs. Charge-Pump Capacitance and Load Resistance graph in the Typical Operating Characteristics. Above 2.2µF, the on-resistance of the switches and the ESR of C1 and C2 dominate.

#### Output Capacitor (C2)

The output capacitor value and ESR directly affect the ripple at PVSS Increasing the value of C reduces output ripple Likewise, decreasing the ESR of C2 reduces both ripple and output resistance. Lower capacitance values can be used in systems with low maximum output power levels. See the Output Power vs. Charge-Pump Capacitance and Load Resistance graph in the Typical Operating Characteristics.

#### Power-Supply Bypass Capacitor

The power-supply bypass capacitor (C3) lowers the output impedance of the power supply, and reduces the impact of the CS4418D s charge-pump switching transients. Bypass PVDD with C3, the same value as C1, and place it physically close to the PVDD and PGND pins.

CHIPSTAR MICROELECTRONICS

CHIPSTAR MICROELECTRONICS Layout and Grounding

Proper layout and grounding are essential for optimum performance.

Connect PGND and SGND together at a single point on the PC board.

Connect all components associated with the charge pump (C2 and C3) to the PGND plane. Connect PVDD and SVDD together at the device. Connect PVSS and SVSS together at the device. Bypassing of both supplies is accomplished by charge-pump capacitors C2 and C3 (see Typical Application Circuit). Place capacitors C2 and C3 as close to the device as possible. Route PGND and all traces that carry switching transients away from SGND and the traces and components in the audio signal path.

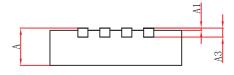

# Package information

# CS4418D QFN 3X3\_16L

**Bottom View**

Side View

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |             |  |  |

|--------|--------------|---------------|----------------------|-------------|--|--|

| Symbol | Min.         | Min. Max.     |                      | Max.        |  |  |

| Α      | 0.700/0.800  | 0.800/0.900   | 0.028/0.031          | 0.031/0.035 |  |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002       |  |  |

| A3     | 0.203        | REF.          | 0.008REF.            |             |  |  |

| D      | 2.900        | 3.100         | 0.114                | 0.122       |  |  |

| E      | 2.900        | 3.100         | 0.114                | 0.122       |  |  |

| D1     | 1.600        | 1.800         | 0.063                | 0.071       |  |  |

| E1     | 1.600        | 1.800         | 0.063                | 0.071       |  |  |

| k      | 0.200        | OMIN.         | 0.008                | 3MIN.       |  |  |

| b      | 0.180        | 0.300         | 0.007                | 0.012       |  |  |

| е      | 0.500TYP.    |               | 0.020                | TYP.        |  |  |

| L      | 0.300        | 0.500         | 0.012                | 0.020       |  |  |

#### Notes:

- (1) All dimensions are in millimeters.

- (2) Complies with JEDEC standard MO-220.